![纪世高等院校计算机科学与技术规划教材:计算机系统结构 《纪世高等院校计算机科学与技术规划教材:计算机系统结构》[53M]百度网盘|pdf下载|亲测有效](/downpdf2/uploads/2024-01-20/280fe136-dd00-4f36-9656-4b256dd98af5.jpg)

![《纪世高等院校计算机科学与技术规划教材:计算机系统结构》[53M]百度网盘|pdf下载|亲测有效](/downpdf2/uploads/2024-01-20/280fe136-dd00-4f36-9656-4b256dd98af5.jpg)

纪世高等院校计算机科学与技术规划教材:计算机系统结构 pdf下载

8.99¥

10.99¥

内容简介

本篇主要提供纪世高等院校计算机科学与技术规划教材:计算机系统结构电子书的pdf版本下载,本电子书下载方式为百度网盘方式,点击以上按钮下单完成后即会通过邮件和网页的方式发货,有问题请联系邮箱ebook666@outlook.com

内容简介

《计算机系统结构》以并行处理技术为主线,介绍计算机系统结构基本概念、基本理论和分析设计的技术方法及其应用实现的逻辑结构模型,讨论指令级高度并行的处理机、向量处理机、阵列处理机、多处理机系统等实现的技术基础、基本结构和性能分析。全书共8章,可分为三部分,第一部分介绍计算机系统结构的基本概念、基本理论和计算机系统结构发展的方向,第二部分介绍流水线技术、指令优化与调度技术、存储组织技术和互连网络技术,第三部分介绍指令级高度并行的处理机、阵列处理机、多处理机系统等。

《计算机系统结构》结构新颖、内容实用、逻辑性强、重点突出、语言精炼,可作为高等院校计算机各专业及相关专业本科生的教材,同时也可作为相关方向的研究生或研究人员的参考书。建议《计算机系统结构》教学用时为70~80学时。

《计算机系统结构》结构新颖、内容实用、逻辑性强、重点突出、语言精炼,可作为高等院校计算机各专业及相关专业本科生的教材,同时也可作为相关方向的研究生或研究人员的参考书。建议《计算机系统结构》教学用时为70~80学时。

精彩书摘

由于地址码低位交叉编址,对连续的地址访问将分布在不同的存储体中,避免了存储体访问冲突。理想情况下,存储器的速度可提高n倍。

4.2.4 无访问冲突存储器

实际上,一个由n个存储体组成的低位交叉存储器的速度并不能提高n倍,其根本原因是存在访问存储的冲突。产生访问冲突的根源主要有两个,一是程序中的转移指令,二是数据被访问的随机性,后者的影响更为严重。以一维数组和二维数组为例,介绍一种多维数组的无冲突访问存储器。

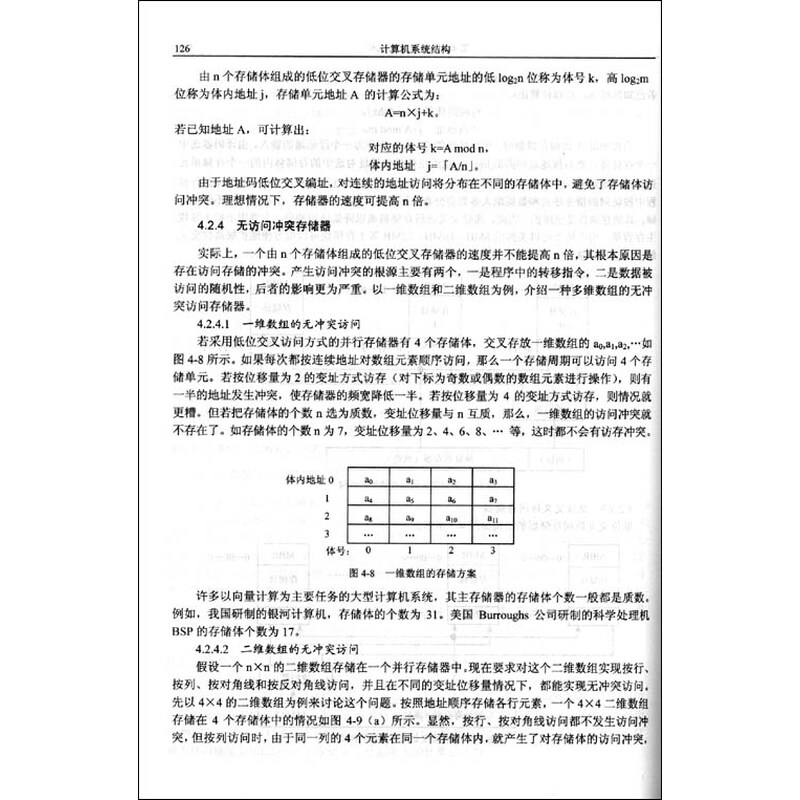

4.2.4.1 一维数组的无冲突访问

若采用低位交叉访问方式的并行存储器有4个存储体,交叉存放一维数组的ao,al,a2,…如图4.8 所示。如果每次都按连续地址对数组元素顺序访问,那么一个存储周期可以访问4个存储单元。若按位移量为2的变址方式访存(对下标为奇数或偶数的数组元素进行操作),则有一半的地址发生冲突,使存储器的频宽降低一半。若按位移量为4的变址方式访存,则情况就更糟。但若把存储体的个数n选为质数,变址位移量与n互质,那么,一维数组的访问冲突就不存在了。如存储体的个数n为7,变址位移量为2、4、6、8、…等,这时都不会有访存冲突。

4.2.4 无访问冲突存储器

实际上,一个由n个存储体组成的低位交叉存储器的速度并不能提高n倍,其根本原因是存在访问存储的冲突。产生访问冲突的根源主要有两个,一是程序中的转移指令,二是数据被访问的随机性,后者的影响更为严重。以一维数组和二维数组为例,介绍一种多维数组的无冲突访问存储器。

4.2.4.1 一维数组的无冲突访问

若采用低位交叉访问方式的并行存储器有4个存储体,交叉存放一维数组的ao,al,a2,…如图4.8 所示。如果每次都按连续地址对数组元素顺序访问,那么一个存储周期可以访问4个存储单元。若按位移量为2的变址方式访存(对下标为奇数或偶数的数组元素进行操作),则有一半的地址发生冲突,使存储器的频宽降低一半。若按位移量为4的变址方式访存,则情况就更糟。但若把存储体的个数n选为质数,变址位移量与n互质,那么,一维数组的访问冲突就不存在了。如存储体的个数n为7,变址位移量为2、4、6、8、…等,这时都不会有访存冲突。

![《年全国计算机等级考试教程三级网络技术》[97M]百度网盘|pdf下载|亲测有效](/downpdf2/uploads/2024-01-20/67d6a57c9fc2d03c.jpg)

![《中文版Photoshop CC基础培训教程 移动学习版》[54M]百度网盘|pdf下载|亲测有效](/downpdf2/uploads/d8fd2e8c75fb303f.jpg)

![《Selenium自动化测试之道——基于Python和Java语言计算机软件开发》[65M]百度网盘|pdf下载|亲测有效](/downpdf2/uploads/0eedccd5d022a218.jpg)

![《分解·归纳:色彩文化创意应用研究计算机与互联网薛毅水利水电书籍》[94M]百度网盘|pdf下载|亲测有效](/downpdf2/uploads/2024-01-20/30575ec63bfc65c9.jpg)